# A Study on Hardware Attacks against Microcontrollers

### Document history

| Version | Date       | Editor | Description   |

|---------|------------|--------|---------------|

| 1.0     | 17.03.2023 |        | Final Version |

|         |            |        |               |

Table 1: Document history

Federal Office for Information Security P.O. Box 20 03 63 53133 Bonn Internet: https://www.bsi.bund.de © Federal Office for Information Security 2021

# Acknowledgement

This report was authored by the Fraunhofer Institute for Applied and Integrated Security (AISEC) on behalf of the German Federal Office for Information Security (BSI).

# Table of Contents

| 1  | Intro    | duction                                       | 6  |

|----|----------|-----------------------------------------------|----|

| 2  | Mark     | et Analysis on the use of Microcontrollers    | 7  |

| 3  | Hard     | ware Attacks                                  | 11 |

|    | 3.1      | Control Flow Manipulation Attacks             | 11 |

|    | 3.1.1    | Countermeasures                               | 12 |

|    | 3.1.2    | Attack Proposal and Countermeasure Evaluation | 13 |

|    | 3.2      | Side-Channel Attacks                          | 14 |

|    | 3.2.1    | Countermeasures                               | 15 |

|    | 3.2.2    | Attack Proposal and Countermeasure Evaluation | 15 |

|    | 3.3      | Read-out Protection Bypass Attacks            |    |

|    | 3.3.1    | Countermeasures                               | 20 |

|    | 3.3.2    | Attack Proposal and Countermeasure Evaluation | 21 |

| 4  | Labo     | ratory Evaluation                             | 23 |

|    | 4.1      | Flash Erase Suppression                       | 23 |

|    | 4.1.1    | Laboratory setup and Results                  | 23 |

|    | 4.1.2    | Conclusion and Future Work                    | 26 |

|    | 4.2      | Compiler-based Fault Injection Protection     | 27 |

|    | 4.2.1    | Attacking MCUboot's RSA implementation        | 27 |

|    | 4.2.2    | Compiler-based hardening of MCUboot           | 29 |

|    | 4.2.3    | Laboratory Setup and Results                  | 31 |

|    | 4.2.4    | Conclusion and Future Work                    | 33 |

| 5  | Conc     | lusion                                        | 35 |

| Bi | bliograj | bhy                                           | 37 |

# List of Abbreviations

| ADC   | Analog-digital converter                                   |

|-------|------------------------------------------------------------|

| AES   | Advanced encryption standard                               |

| ANSSI | Agence Nationale de la Sécurité des Systémes d'Information |

| COTS  | Commercial off-the-shelf                                   |

| CPU   | Central processing unit                                    |

| CRC   | Cyclic redundancy check                                    |

| ECC   | Elliptic curve cryptography                                |

| ECC   | Error correction code                                      |

| EM    | Electromagnetic                                            |

| EMFI  | Electromagnetic fault injection                            |

| FCC   | Federal communications commission                          |

| FIB   | Focused ion beam                                           |

| GPIO  | General-purpose input/output                               |

| IoT   | Internet of things                                         |

| IP    | Intellectual property                                      |

| IR    | Intermediate representation                                |

| ISA   | Instruction set architecture                               |

| LFI   | Laser fault injection                                      |

| NDA   | Non-disclosure agreement                                   |

| OTA   | Over-the-air                                               |

| PC    | Program counter                                            |

| POS   | Point-of-sale                                              |

| ROP   | Return-oriented programming                                |

| RSA   | Rivest-Shamir-Adleman                                      |

| SNR   | Signal noise ratio                                         |

| SRAM  | Static random-access memory                                |

| TTM   | Time to market                                             |

|       |                                                            |

- USB Universal Serial Bus

- UV Ultra-violet

- XOM Execute-only memory

# 1 Introduction

Microcontrollers are widely used in numerous applications such as robotics, medical devices, aerospace, and automotive. Concepts such as the internet of things (IoT) further increase their pervasiveness in areas within industrial and consumer products. Since microcontrollers are responsible for complex tasks they contain valuable intellectual property (IP) that could be of interest to competitors and are therefore worth protecting. Furthermore, microcontrollers can be found in sensitive applications such as access control systems. As a consequence, they contain credentials and other cryptographic secrets which make them an attractive target for adversaries. For that reason, the security of microcontrollers and their respective assets are of utmost importance for today's applications.

This security must be carefully evaluated. For one, threats known for other computer systems such as desktops and servers also apply to microcontrollers. Additionally, there is an attack type, which can be ignored in many cases for desktop and server platforms: the hardware attack. Due to their pervasiveness and accessibility, hardware attacks and their countermeasures must be taken into special consideration for microcontrollers. Other computing systems are less easy to access for adversaries, therefore hardware attacks are less relevant but not completely negligible. Despite restrictions, an attacker might gain access to the device or induce hardware attacks remotely. However, this report focuses on hardware attacks on accessible microcontrollers and does not further consider other computing systems. Hardware attacks are often not part of the threat model of microcontroller manufacturers, but nevertheless, these attacks are frequently reported and need to be addressed. Vulnerabilities on the hardware level allow the adversary to mount attacks, regardless of the application software.

There exist security controllers with built-in protections against hardware attacks and satisfy certain assurance levels assessed by independent evaluation laboratories [2]. However, commercial off-the-shelf (COTS) microcontrollers are prevalent in security relevant IoT products. The reasons are manifold but in the end mostly price-driven. COTS devices are mostly cheaper and easier to acquire. In contrast to security controllers where usually a non-disclosure agreement (NDA) is required for detailed product information, COTS microcontrollers benefit from publicly available tools, documentation, and code which accelerates development and time to market (TTM). Finally, microcontroller manufacturers and product designers have limited awareness of potential threats through hardware attacks. Manufacturers are gradually starting to build countermeasures against hardware attacks into some of their product families. However, these devices only slowly find their way into products, while devices which are already deployed in the field remain vulnerable to this kind of attacks. Therefore, effective countermeasures, particularly those that can be retrofitted into existing devices are important for products already in circulation.

This report is meant to create awareness for hardware attacks on critical infrastructure that is built upon COTS microcontrollers. After reading, both technical-proficient and non-proficient readers should be able to judge the threat posed by unprotected implementations . First, an overview of COTS microcontrollers which are used in security relevant IoT products is given. An online market analysis based on publicly available information was conducted to substantiate the relevance of microcontrollers for such products. Further, this report gives an overview of state-of-the-art hardware attacks against microcontrollers. Based on a literature research, the most important attack vectors are elaborated and summarized. Three hardware attacks and suitable countermeasures that are of interest for further investigation are proposed. As mitigation, software-based countermeasures that can be retrofitted for such devices with minimal cost and without a significant degradation of performance or user experience are promoted. As long as hardware countermeasures are only slowly adapted for COTS microcontrollers, software countermeasures are the only way to protect products from hardware attacks. The report concludes with a laboratory analysis where two of the proposals are practically evaluated. The results demonstrate the effectiveness of software countermeasures and are meant to motivate vendors to consider these countermeasures for their products.

# 2 Market Analysis on the use of Microcontrollers

In order to understand which microcontrollers are used in security-relevant products, a market analysis is conducted. The analysis is based on different product categories to estimate the share of microcontrollers and manufacturers across application domains.

**Market Analysis.** The starting point for the market analysis is a list of microcontroller manufacturers that was created in the course of the work of Fraunhofer AISEC in the field of hardware security. To avoid a possible bias or forgetting manufacturers, this list was compared and completed with an independent and public list of microcontroller manufacturers [4]. From these manufacturers a list of product categories they propose for their devices was obtained. These categories are boiled down to those where microcontrollers are used in a security-relevant context. For each application, representative products are taken into account and their internals are investigated. Since product manufacturers rarely provide publicly available information about integrated components such as microcontrollers, other sources are used. This includes but is not limited to publicly available teardowns of products by the FCC and researchers in forums, blogs, and journals. Our findings are condensed into overview tables for the respective sections on product categories.

It is important to note that our market analysis does not represent the exact and complete distribution of microcontroller devices in a product category. There are multiple reasons for this: first, the fact that manufacturers hardly ever publish information on integrated components, as already mentioned. Second, the sources that are consulted for these information instead do not fully reflect the market. Pricing, availability, and popularity make certain products more likely to appear in public teardowns. Naturally, this could lead to a potential over- or underrepresentation of certain vendors in our market analysis. But even if the study does not paint the complete picture, it suffices for the reader to accurately judge the threat of hardware attacks in the identified categories. For all categories, products incorporating microcontrollers by four or more different vendors were found. The identified microcontrollers are of similar price ranges and capability levels. None of these include dedicated countermeasures against hardware attacks. Therefore, most products of the respective categories are expected to feature identical or similar microcontrollers and the subsequent listings are considered to be representative within this study.

The following applications were identified across vendors and are deemed most relevant for this study:

- hardware security tokens

- hardware crypto wallets

- smart locks

- point-of-sale (POS) terminals

Adversary Model. It is assumed an adversary that has either the incentive to extract intellectual property (IP) or cryptographic secrets. The consequences of such an attack can be of economic relevance, e.g. stealing from an economic competitor, or security relevance, e.g. compromising critical infrastructure, or both, e.g. compromising critical infrastructure to harm a competitor. However, the exact intentions behind IP theft or extraction of cryptographic secrets are not further explored in this report.

For the extraction of cryptographic secrets the attacks launched can be further classified as supply chain attack, evil maid attack, or straightforward theft:

- A supply chain attack targets the delivery of products. The adversary can either compromise the shipped device or ship own malicious devices which seem to behave like an original device.

- If a product is already in use an attacker may compromise it in an evil maid fashion or try to steal it. The evil maid scenario is defined by the fact that the adversary has only access for a limited time and

tries to avoid changes to the outer appearance or observable behavior of the device. In this case, if the user of a device leaves it out of sight temporarily, i.e. a few minutes up to a day, the attack of the evil maid is not detected.

• If the adversary steals the device, the time span for attacks is longer and damages to hardware or software are unimportant. However, in certain scenarios, the victim can take action to invalidate the cryptographic secrets stored on the device if the theft is detected.

Within these three attack types, an adversary has the possibility to indirectly or to directly extract secrets. The direct approach allows the adversary to immediately extract secrets by circumventing existing countermeasures. Depending on the application, this attack can be used in all three attack types. In contrast, the indirect approach is to tamper the functionality. This can lead to the insecure usage of cryptographic algorithms, which is then exploited by an attacker. Since the attacker has to use the device after the modification to be effective, only evil maid and supply chain attacks are possible. For example, forcing the product to use a low-quality or even static source of randomness can lead to easy-to-guess keys, which may be brute-forced by an attacker in a second step. Further, this allows to influence the overall behavior of the product, which leads to a security compromise. For instance, if the product does no longer verify the authenticity and integrity of a request, which shall be assured cryptographically.

**Hardware Security Tokens.** Hardware security tokens are used for authentication to web or local services. They can be used as a single or second factor. A single factor authentication is used for the so called password-less authentication. Due to the ease of use this method is becoming increasingly popular. The fact that the security relies on a single secret stored on the device makes the token particularly interesting for an adversary. Compromising the hardware token is sufficient for a successful authentication. In general, hardware security tokens store attestation keys as well as service keys, which are both of interest for an adversary. Besides the keys, the functionality to generate new keys is also of interest. The attestation keys are long-term secrets, which are loaded by the manufacturer or are created by the device itself during production. These are used to attest the authenticity and integrity of a device to a user or a service. If an attacker has access to such attestation keys, they would be able to ship own devices, which generate valid attestation proofs. The service keys are run-time secrets, which are loaded by the user or created by the device itself during the usage, for instance, secrets specifically used to gain access to a service. Having knowledge about service keys would allow to authenticate against a service without being in possession of the respective hardware security token. This would undermine the security guarantees given by hardware security tokens.

| Vendor                   | Device Family | Product                   |

|--------------------------|---------------|---------------------------|

| Microchip (former Atmel) | AT32UC3A      | Nitrokey Storage 2        |

| STMicroelectronics       | STM32F1       | Nitrokey Start            |

|                          |               | Nitrokey Pro 2            |

|                          |               | Nitrokey HSM 2            |

|                          | STM32L4       | Nitrokey FIDO2            |

|                          |               | SoloKeys Solo 1 USB-A     |

|                          |               | SoloKeys Solo 1 USB-C     |

|                          |               | SoloKeys Solo 1 Tap USB-A |

|                          |               | SoloKeys Somu             |

| NXP                      | LPC55S6       | Nitrokey 3                |

|                          |               | Solokeys Solo 2A+         |

|                          | Kinetis       | OnlyKey OnlyKey           |

|                          | LPC11Uxx      | Google Titan Security Key |

| Silicon Labs             | EFR32BG13     | Certgate AirID FIDO       |

Table 2.1: Hardware security tokens and their integrated microcontrollers found in the market analysis.

The results of the market analysis, summarized in Table 2.1, show that mostly microcontrollers from STMicroelectronics or NXP are used within hardware security tokens. Only few devices are based on microcontrollers from Microchip or Silicon Labs.

**Hardware Crypto Wallets.** While the actual record of crypto currency is stored in a public blockchain, the secret key that provides access to the actual owner must be stored securely in a crypto wallet. Any transaction like transferring the currency requires a user authentication with this key. If needed, the crypto wallet can also generate new keys for future transactions. An adversary who gains illegal access to a user's secret key can use the cryptocurrency as they please, e.g. transfer it to herself. The economical value protected by crypto wallets is not technically limited. This makes crypto wallets interesting targets for an attacker.

Crypto wallets can be implemented in software, but often hardware wallets are used, as attacks on hardware wallets require physical access. An adversary is interested in all attacks that allow them to extract the secret key without being the actual owner of the wallet. In addition, they also profit from gaining the ability to generate new keys. Manufacturers of hardware crypto wallets are aware of attacks and especially supply chain attacks. Hence, to encounter these they modify the packaging, add seals, and harden the firmware of their devices [3].

Table 2.2 shows device families of microcontrollers that are commonly used in hardware crypto wallets. A large market share is taken up by microcontrollers from STMicroelectronics. Otherwise, microcontrollers from Microchip, Mediatek, and Ambiq were found to be parts of hardware crypto wallets.

| Vendor                   | Device Family | Product                     |

|--------------------------|---------------|-----------------------------|

| Microchip (former Atmel) | SAM D51       | Shiftcrypto BitBox02        |

| STMicroelectronics       | STM32F0       | Ledger Nano S               |

|                          | STM32F2       | Trezor One                  |

|                          |               | Shapeshift keepkey          |

|                          |               | ProKey Wallet               |

|                          |               | ProKey Optimum              |

|                          | STM32L4       | Coinkite Coldcard Mk3       |

|                          | STM32L4+      | Coinkite Coldcard Mk4       |

|                          | STM32H7       | Foundation Passport Batch 2 |

|                          | STM32WB       | Ledger Nano X               |

|                          |               | Keevo Model 1               |

|                          | STM32MP1      | NGRAVE ZERO                 |

| Mediatek                 | MT6850        | Keystone Essential          |

| Ambiq                    | Apollo3       | Hashwallet                  |

Table 2.2: Hardware crypto wallets and their integrated microcontrollers found in the market analysis.

**Smart Locks.** Nowadays, modern access control systems are often built with the help of smart locks. Smart locks enable the facility management to dynamically update access rights, for example for new employees. This also implies that secret information used by new employees to authenticate themselves must be frequently integrated into the system. If an adversary is able to integrate arbitrary keys into the system they would gain unauthorized access to the facility. In addition, the successful cloning of existing keys would give them the opportunity to intrude while impersonating an authorized person.

The results of the market analysis summarized in Table 2.3 show that microcontrollers from Microchip, STMicroelectronics, Silicon Labs, Infineon, Texas Instruments, or Telink Semiconductor are used within smart locks. In contrast to the other analyzed product categories, there is no major vendor of microcontrollers in this category.

| Vendor                   | Device Family | Product                       |  |

|--------------------------|---------------|-------------------------------|--|

| Microchip (former Atmel) | PIC18F87K22   | Schlage Sense Smart Deadbolt  |  |

|                          | PIC16F1938    | MiLocks Keyless Entry         |  |

|                          | AT91RM3400    | Simon Voss Entry Transponder  |  |

| STMicroelectronics       | STM32L1       | August Smart Lock             |  |

| Silicon Labs             | EFM32 Gecko   | Salto XS4 One                 |  |

|                          |               | Salto XS4 Mini                |  |

| Infineon                 | PSoC 1        | Unknown Product               |  |

|                          | PSoC 6        | August Smart Lock             |  |

| Texas Instruments        | TI MSP430     | Schlage Connected Keypad Lock |  |

| Telink Semiconductor     | TLSR825X      | OASBIKE Bluetooth Smart Door  |  |

|                          |               | Lock                          |  |

Table 2.3: Smart locks and their integrated microcontrollers found in the market analysis.

**POS Terminals.** Point-of-sale terminals are the standard way of processing payments in the retail industry. Typically they do not store secret information that is of interest for an adversary. Instead, tampering attacks that alter the original functionality of the terminal are a potential threat for these devices. For example, the customer must trust the information shown on the display integrated into a POS terminal, i.e. the amount to be paid. Therefore, any compromise which gains control over the display would enable fraud. This is the case because the amount shown on the display and the amount charged from the card may not match. An attacker could charge more from the card than the customer is aware of. Thus, the customer loses the opportunity to verify the amount to be charged before the transaction is carried out.

The results of the market analysis in Table 2.4 show that mostly microcontrollers from NXP, STMicroelectronics, Maxim Integrated or Nordic Semiconductor are used within POS terminals.

| Vendor               | Device Family | Product                   |

|----------------------|---------------|---------------------------|

| NXP                  | Kinetis K22   | Square POS                |

|                      |               | Square Reader             |

|                      | i.MX258       | Nexgo G3N                 |

| STMicroelectronics   | STM32F0       | Square POS                |

|                      |               | Square Reader             |

| Maxim Integrated     | MAX32550      | SumUp Air                 |

|                      |               | Sagem Monetèl ETF930S-GEM |

|                      | DS5240        | Sagem Monetèl ETF930S-GEM |

| Nordic Semiconductor | nRF52         | SumUp Air                 |

Table 2.4: POS terminals and their integrated microcontrollers found in the market analysis.

### 3 Hardware Attacks

The following chapter lays out attack classes that were deemed most relevant for hardware attacks on microcontrollers. The attack classes were selected from contemporary research on hardware attacks published in journals or blogs and presented on conferences. As stated in Chapter 2, threats posed by IP theft, evil maid adversaries, supply chain attacks, and device theft are the focus of this report. Therefore, the attack classes were chosen accordingly to these scenarios. For each attack class, a concrete attack proposal and evaluation of countermeasures is proposed.

### 3.1 Control Flow Manipulation Attacks

The control flow of an application determines the order in which instructions are executed. Control flow attacks aim to modify the flow of execution of a program in a way that benefits the adversary. Manipulating the control flow opens various possibilities to undermine the security of a system. For example, it allows the adversary to execute code which requires higher privileges, or to deliberately prevent code execution. In the latter case, the adversary can, for instance, circumvent password checks and thereby gain higher privileges.

A widely known entry gate to mount control flow attacks are buffer overflows, which can corrupt the return address on the stack. This vulnerability allows the adversary to mount a return-oriented programming (ROP) attack and thereby arbitrary code execution on a target, as the return address determines the instructions to be executed after returning from a function call. ROP and related attacks require a vulnerability in the application code that can be exploited by the adversary. While these vulnerabilities are often reported, they can be mitigated by the use of safe programming languages such as Rust. However, at the moment, the Rust support for microcontrollers is mainly community-driven and far from being as comprehensive as the support for the C programming language.

For embedded devices and microcontrollers where physical attacks are possible, control flow manipulation attacks do not require vulnerabilities in the application code. Instead, hardware attacks such as voltage and clock glitching, electromagnetic fault injection (EMFI) and laser fault injection (LFI) can be used to manipulate the control flow of an application.

Fault attacks are used for causing erroneous behavior such as:

- Bypassing the execution of either a specific instruction (single instruction skip), or multiple contiguous instructions (multiple instruction skips)

- Corrupting data on memory or during a bus transfer

- Replacing an instruction with another one, i.e, instruction modification

- Tampering of the program counter

This erroneous behavior is then exploited by the adversaries in order to gain privileges, bypass security measures, extract information, inject malware and more.

Current literature includes numerous examples of successful fault injection attacks on commercial components and devices. Those include, for example, circumventing the memory protection via fault injection for enabling the extraction and subsequently reverse engineering of automotive firmware [65]. Another example is the extraction of a secret key used in an AES core by manipulating the core configuration in [53],[56]. In [84] the authors manage to escape from a TrustZone with the help of fault injection attacks, and in [67] the authors show how fault attacks can be used to generate buffer overflows and demonstrate a complete exploit with a subsequent software attack. Voltage glitching was used in [14] to skip security checks in the bootloader of various microcontrollers and therewith bypass the memory protection. Similarly, in [70],

instruction skips are used to skip bound checks in USB stacks and exploited to perform an out-of-bounds read and to dump credentials.

#### 3.1.1 Countermeasures

In order to protect microcontrollers against control flow manipulation, several software and hardware countermeasures have been proposed [8],[9],[29],[30],[35],[37],[51],[73],[74],[80],[81],[90],[97]. The aim of those countermeasures is the avoidance, detection and/or correction of control flow attacks.

Software-based countermeasures have the advantage that no special hardware is required and retrofitting may be supported via software updates. Nonetheless, it is not always possible to protect against hardware attacks with software-based countermeasures, as faults are introduced directly into the underlying hardware.

According to their point of integration, control flow protection techniques can be divided into four different categories:

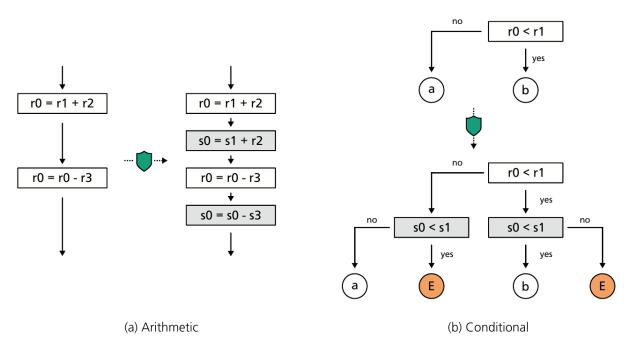

- Source code countermeasures: At the source code level, software countermeasures are added through a high-level programming language, e.g. the C language. For example, intra-procedural jump attacks could be detected by inserting routine-calls into protected code. Those routines would then check and increment a counter before the next line of code is executed. The disadvantage of this type of countermeasures is that compiler optimizations may have to be disabled in order for the countermeasure to remain present after compilation. Another drawback is that this technique increases the code base and the complexity developers have to deal with.

- *Compiler-based countermeasures:* Unlike source code countermeasures, the protection added by compiler-based countermeasures is guaranteed to be present in binary form, because of the compiler being explicitly aware of its presence. Compiler-based countermeasures make use of the different representations that a program goes through before having a target-specific representation, i.e. binary form. The most convenient representation for the addition of control flow protections is the so called intermediate representation (IR), which is language and architecture independent. However, the underlying platform architecture still has to be considered for a robust and efficient inclusion of countermeasures.

- Post-compilation countermeasures: Post-compilation countermeasures refer to the addition of control flow protections to the binary form at the machine language level, i.e. assembly language. This may, for example, involve the addition of redundant instructions, which have the exact same functionality and guarantee the same computational outcome, even when instructions are skipped. The downside of such techniques is the added overhead regarding code size and execution time with respect to compiler- based countermeasures. This is due to countermeasures being added at a point, at which processor registers and memory addresses have already been allocated, thus requiring the addition of intermediate variables and branches to the existing binary. While source code and compiler-based countermeasures are already market-ready and applied in real-world products, post-compilation countermeasures are more a research topic. Due to the lack of automated tools and the manual effort required of developers, their use is not known outside the research community.

- *Hardware-based countermeasures:* Those are countermeasures that involve the modification of the system hardware, for example addition of hardware peripherals or modification of the instruction set. Compared with their software counterparts, hardware-based countermeasures have less impact on the system performance, as they don't demand execution time from the CPU. However, they are expensive to implement and of course cannot be retrofitted into existing platforms via software updates.

After laying out the four general categories based on the point of inclusion, different techniques for hardening software against hardware attacks tampering with the control flow are described. These

techniques may fall into one or more of the four categories introduced above, depending on the implementation layer they are applied on.

- *Classic Loop Hardening:* This technique relies on duplicating the loop counters and exit conditions, such that the condition has to be checked twice before exiting the loop [78]. By comparing the redundant loop counters, it is then possible to detect fault injection attempts.

- *Instruction Redundancy:* This technique involves the execution of critical instructions at least twice, i.e. instruction duplication, in order to provide the same computational result even if instructions are skipped [9]. The redundant instructions must be idempotent, i.e. instructions which can be executed several times while providing the same result as when executed only once. For non-idempotent instructions, an equivalent has to be found, which greatly increases the amount of instructions and often involves the use of additional registers. However, depending on the threat model, the duplication of instructions may still be insufficient, as some hardware attacks are able to skip multiple instructions at once, as demonstrated in [35], where skips of up to 6 consecutive instructions were achieved.

- *Redundant-Encoded Data:* This technique is based on encoding data in order to prevent memory corruption and protect memory transfers [37]. The encoding projects the value of the data into a broader value range, thus facilitating the detection of manipulations.

- *Global Signature Register:* This technique divides memory in basic blocks and performs signature checks when transitioning between them, thus being able to detect control flow deviations between basic blocks [81].

- *Redundant Computation:* This technique relies on computations being executed twice, using different sets of registers, in order to detect instruction skips and register corruption. It was first proposed in [74] and enhanced in various works presented in recent years [29],[30],[81]. The newest implementation of this technique is presented in [90], where the authors state that control flow corruption inevitably leads to data corruption, thus making data corruption detection a mean for detecting control flow corruption.

- *Variable Duplication:* This technique is based on duplicating all variables and their respective read/write operations [80]. Write operations are performed on the original variable and on its duplicate, while read operations are always followed by a comparison of both variables.

- *Function Duplication:* This technique comprises the duplication of a function. The inputs given to both functions are the same, but the results are stored in different variables and compared after both have been executed [8]. A fault attempt is detected if the results of both functions do not match. An enhancement of this technique is the use of equivalent, non-identical duplicate functions, in order to decrease the probability of an attack being successful on both functions.

- *Statement Counters:* This technique refers to the addition of counters and checks between portions of code, e.g., functions, loops, single lines of code [51]. The value of the counters indicate if the statements are executed in the right order, and fault attempts are identified by the presence of unexpected counter values, i.e. a counter increment was skipped.

#### 3.1.2 Attack Proposal and Countermeasure Evaluation

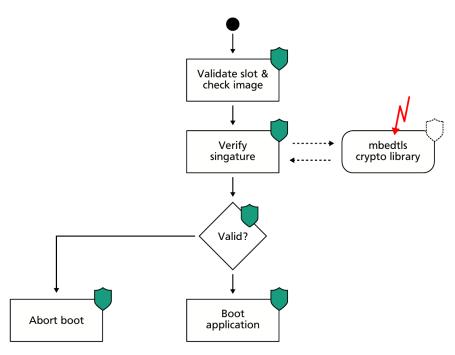

Due to their potential for bypassing security measures and embedded protections such as secure boot and memory bound checks, a demonstration of fault injection attacks causing instruction skips on microcontrollers is part of this report. This section establishes the practical attack and countermeasure evaluation and its relevance to control flow attacks in general. The laboratory demonstration is described in Section 4.2.

For demonstrating those faults, EMFI [70] on STM32L4 microcontrollers seems a promising approach. This is due to STM32 being one of the most relevant families of microcontrollers for all considered product categories, as shown in the market analysis in Chapter 2.

The proposed countermeasure to evaluate is the software-based redundant computation presented in [90], which targets data flow and control flow corruption. As described above, it builds on the assumption that control flow manipulation leads to data corruption. First, works on redundant execution that laid the foundation for [90] such as [29],[30],[74],[81] and pure control flow protection approaches such as [73],[97] are revisited. This is deemed necessary, as all these works were driven by safety-focused research, and therefore their findings can not be directly applied to security. The results of this evaluation are presented in Section 4.2.2.

For future work, further analysis of techniques to protect memory contents are proposed. The authors of [90] rely on ECC memory protection to ensure instruction and memory integrity. If no ECC hardware is available, as is often the case on COTS devices, an attacker could still tamper memory contents. A possible mitigation of this attack vector is the insertion of encoded data during compile time in order to protect data in memory and bus transfers. For such a compiler extension, different coding schemes should be evaluated regarding their detection capabilities and performance overhead. Ideally, at some point in the future, all these efforts can be combined into a framework that hardens software for arbitrary COTS microcontrollers without having any constraints on the underlying hardware. Therefore, retrofitting firmware for existing products is also possible.

### 3.2 Side-Channel Attacks

Side-channel attacks are passive attacks that exploit information emitted due to the fundamental way an algorithm is implemented. Among others, cryptographic systems have been broken with timing [50], power [49], and electromagnetic [79] side-channel information. For microcontrollers, power and electromagnetic emission are the most critical side-channel information an attacker can exploit. On the one hand, this is due to the absence of data caches on such systems and the availability of constant-time cryptographic algorithms, both of which avoid leakage through the timing side-channel. On the other hand, an attacker can easily gain physical access to a microcontroller to measure power and electromagnetic emission. Power measurements might require physical modifications such as the integration of measurement elements into the power supply path or the removal of decoupling capacitors. This makes them less applicable to evil maid and supply chain scenarios. However, EM measurements are typically non-invasive and can be carried out in these scenarios.

The target of side-channel attacks is typically to obtain a cryptographic secret. If known to the attacker, the secret allows them further attacks such as impersonation of the device, sending of malicious information, or IP theft. This is extremely critical, as microcontrollers often control physical assets. Even if an attacker has to spend a lot of effort regarding time and equipment, the attack might pay off. This was demonstrated in a resounding fashion by Ronen et al. in [83]. The authors could extract the global AES-CCM key for a Philips Hue smart lamp. This key was responsible for verifying the authenticity of OTA firmware updates. Their attack would have allowed an evil adversary to build authentic but malicious firmware images and compromise the entire wireless network of Philips Hue smart lamps. For example, an adversary could have turned off all bulbs in an area such as Paris, where the number of devices exceeds a critical mass.

A demonstration in [72] showed that side-channel attacks are possible in contexts one might not necessarily expect it. O'Flynn and Dewar use on-chip side-channel analysis to measure cryptographic secrets used by the trusted domain of a device. For this the authors run code in the untrusted domain that utilizes the ADC to obtain side-channel measurements. So while most power and electromagnetic side-channel attacks are conducted in a setting where the adversary has access to the device and lab equipment, this is not

necessarily required. The attack is demonstrated on the AES peripheral used within the ARM TrustZone of a Microchip SAML11 microcontroller.

Straightforward power and electromagnetic side-channel attacks on unprotected software implementations running on microcontrollers are frequently reported. The efforts in [49],[66],[71] are only a few of the papers published on this. All these works demonstrate the rather obvious fact that unprotected software must not be run on simple microcontrollers, if an adversary can gain access to secret information over the power or electromagnetic side-channel.

#### 3.2.1 Countermeasures

Since power side-channel information was first used by Kocher et al. [49] in 1998, researchers have investigated different countermeasures and their effectiveness. Among these countermeasures, masking [24],[36],[42] stands out due to efforts in formalizing attacker models and implementations that can withstand them. This allows designers to judge the security level of their implementation. An effort to standardize masking schemes was recently initiated [15].

Masking schemes apply random masks to secret values in order to create secret shares, which are subsequently used for the cryptographic computations. In *d*-order masking, d + 1 shares are used. All but one share can be sampled from a uniform random distribution. These are the so-called random masks. The final share is chosen such that recombining the shares yields the original secret. A related technique to masking is blinding. In contrast to masking, blinding uses algorithmic approaches to mask sensitive values. For RSA and ECC, scalar [76] or exponentiation blinding [50] can be used to avoid leakage of secret exponents.

In contrast to masking which hides the actual values, shuffling [44] hides the order in which values are processed. Operations are scheduled randomly, which hides correlations of side-channel measurements with secret information.

Another approach to defend against power and electromagnetic side-channel attacks is leakage resilient cryptography [63]. Its underlying rationale is to limit the exposure of the secret key such that an attacker has limited capabilities in accumulating information over multiple observations. It has been applied successfully to cryptographic implementations on microcontrollers in [96]. In contrast to masking and shuffling, no randomness is required. Leakage resilient cryptography is therefore also highly relevant for retrofitting countermeasures to microcontrollers. The work conducted in [96] could be extended by considering the latest leakage resilient schemes such as ISAP [31]. However, this report focuses on the application of masking for the countermeasure evaluation proposed in the next section. The continued analysis of leakage resilient cryptography on COTS microcontrollers is left open for future efforts.

Apart from the masking, shuffling, and leakage resilient countermeasures, which include formalized knowledge on an attacker's capabilities, there are several obfuscation approaches often referred to as hiding. An example for a hiding-based approach is the installation of random stall or dummy operations and additional noise sources to reduce the SNR [93]. Since the resilience of these approaches is hard to put into concrete terms they are mostly used in combination with masking or shuffling. Another approach to hide power and electromagnetic side-channel information are dedicated logic encodings, e.g. dual rail logic. Dual rail implementations balance the power consumption regardless of the processed value [85]. However, implementations are costly and vulnerable to attacks based on different propagation times [46].

#### 3.2.2 Attack Proposal and Countermeasure Evaluation

Due to the clear focus on masking by the research community it is also the focus of protecting microcontrollers against side-channel attacks for this report. Masked software implementations would

allow retrofitting side-channel resilience to COTS microcontrollers. It should be emphasized that leakage resilient cryptography is also an established method in protecting against side-channel attacks. Its suitability for retrofitting side-channel protection to microcontrollers featuring generic unprotected AES hardware accelerators has been explored successfully in [96].

There are two approaches to measure the resilience of a masked implementation. The traditional approach is to rely on standardized laboratory work [33],[34],[89]. This requires massive effort and recent works have shown that standardized tests are not guaranteed to find weaknesses [16].

A newer approach was brought forward in [77]. In this work, Prouff and Rivain present a formal proof of the information leakage in masked implementations. Since then, several formal proofs and works that try to bridge the gap between these theoretic proofs and the actual capabilities of an adversary with more realistic models were published [13],[23],[43]. In [20],[25],[64],[94] various authors show that attacks on naive masking implementations are easier than originally thought. Formal approaches could have shown these vulnerabilities without requiring costly evaluations in the laboratory. However, in [12], Battistello et al. show an attack on an implementation that was deemed secure in a formal model. Wrong assumptions on the model made attacking the implementation a lot easier than originally thought. This shows that the maturity of formal approaches must increase so that they can be put to practical use. Nonetheless, there is massive potential in their application to security evaluations.

Research in both formal approaches to masking and attacks on masked implementations has seen a massive attention gain in recent years. Attacks on masked implementations can be divided into two categories. Each category represents a challenge in implementing masking on microcontrollers correctly. Attacks of the respective category exploit shortcomings in meeting this challenge.

Low physical Noise of Microcontrollers. Microcontrollers suffer from low physical noise. Among others, this is due to their nature of sequentially executing one instruction after the other. Thus, an attacker can easily obtain patterns related to secret information from power or electromagnetic side-channel measurement traces. In [16], Bronchain and Standaert attack a hardened AES implementation proposed by the French ANSSI. They show that by means of advanced statistical post-processing, the full key can be recovered with less than 2,000 measurements. Limited noise in the attacked ARM Cortex-M4 (ATSAM4LC4CA) is the primary cause for this security flaw. The authors propose a significantly higher number of shares to counteract this limitation. Additionally, the authors make an interesting point on closed source security evaluations. A preliminary leakage assessment of the implementation by ANSSI did not detect dependencies between traces and secret data in up to 100,000 traces. With their advanced attacks, the authors were able to recover the key with significantly less. In [60], Masure and Strullu extend the work by [16] with new attacks and a public data set of traces. Similar to [16], Udvarhelyi et al. [95] show an attack on a hardened implementation of the lightweight crypto algorithm ISAP [32]. Their target is an ARM Cortex-M0 (STM32F0) that also suffers from low physical noise. In [17], Bronchain and Standaert attack higher-order masked implementations of AES and the lightweight crypto scheme Spook / Clyde [22]. Their target platforms are an ARM Cortex-M0 (STM32F0) and an ARM Cortex-M3 (STM32F100) microcontroller. A 6-share AES implementation on the Cortex-M0 was demonstrated to be broken with 10 traces and a 5-share AES implementation on the Cortex-M3 with 1000 traces. Only an 8-share implementation of Clyde on the Cortex-M0 could not be broken with less than 50,000 traces. They evaluate their findings in a formal model [43] and demonstrate that the model shows the same results if it is instantiated with realistic noise parameters. Gohr et al. [40] evaluate attacks on the same traces of Spook / Clyde with deep learning and achieve a similar efficiency as [17].

**Micro-architectural Leakage.** In [7], Balasch et al. show an implementation that provides significantly less side-channel resilience than expected because the actual architecture of the implementation and its leakage through micro-architectural transitions are not considered. An example for such a transition is if a share in an internal register (e.g. in the load-store unit) is overwritten with another share. Balasch et al. compare a masked C implementation and a masked assembly implementation that considers architectural leakage of an Atmega163 and an 8051 microcontroller. They demonstrate that the security order of the C

implementation reduces by factor two if a more realistic model that takes transitions into account is considered. Gao et al. [38] show a similar effect for share sliced implementations on an ARM Cortex-M0 (NXP LPC 1114) and ARM Cortex-M3 (NXP LPC1313). In [75], Papagiannopoulos and Veshchikov study the micro-architectural leakage effects of an Atmega163 in more depth and propose a tool to verify AVR assembly code for such effects.

This is only one of many verification tools for masked implementations that have been proposed by researchers in recent years [10],[11],[26],[39],[48],[62],[92],[98]. The works differ in the theoretic model they rely on, the architecture they provide verification for, the architectural leakage effects they consider and whether they can be used for hardware or software masking. A complete systematization of knowledge on design tools for side-channel aware implementations can be found in [21]. More information on theory and application of masking in general can be found in the survey by Covic et al. [27]. Marshall et al. [59] published an interesting study of different micro-architectural leakage effects on different microcontrollers.

Formal verification of masked implementations can potentially provide a high resilience against sidechannel attacks without arduous and possibly erroneous laboratory evaluations. However, as of now, the gap between theoretic proofs, realistic noise levels, and realistic leakage due to micro-architectural effects is too wide. For future evaluation, an attack and countermeasure demonstration is proposed to close this gap.

**Practical Evaluation.** The attack on higher-order implementations of AES by Bronchain and Standaert in [17] is one of the most fatal attacks as they achieve a complete key recovery with very few traces. They connect their findings to a formal model [43] and identify the low amount of noise on STM32F0 and STM32F100 microcontrollers as the primary weakness. However, they do not consider leakages caused by micro-architectural effects. It remains unclear how much harder the attack gets if these leakage effects are taken into account and are mitigated. Further, the authors assume very strong attacker capabilities like profiling with known randomness. This decision is backed by the reasoning from [6], as making worst case assumptions on the attacker provides a reliable and safe way to evaluate countermeasures. If a countermeasure is effective against the worst case attacker (e.g. one that can profile with known randomness), it is guaranteed to hold up against attackers with less capabilities. However, this implies that countermeasures are more expensive in terms of performance than they need to be in the face of realistic adversaries. This leaves room for further evaluations. Recent work by Masure et al. proposes a threat model for so-called scheme-aware attackers, which makes more realistic assumptions on an adversary's capabilities, while still providing a reliable and safe way to evaluate countermeasures [61]. Within this model, adversaries know the implemented scheme and countermeasures from high level source code all the way to the actual machine code and its execution trace (i.e. what happens when), but they do not have access to internal resources such as the randomness generated by the internal random number generator. Future work that evaluates existing attacks and countermeasures against such a threat model would provide valuable insights for retrofitting countermeasures to COTS microcontrollers.

The attack published by Bronchain and Standaert in [17] is a promising starting point for such an evaluation. Their evaluation could be extended by protecting the AES implementation against micro-architectural faults that cause leakage. The *scVerif* tool [11] can be used to detect such faults in the AES code. In [5], Abromeit et al. propose a compiler built on top of the *scVerif* tool that automatically generates correctly masked software. Unfortunately, the compiler was not made publicly available for further evaluation.

The verified implementation is then again attacked with the proposed attack by Bronchain and Standaert. In addition, other attack approaches from [18],[19],[40],[58] can be adapted for a thorough evaluation. This puts the leakages caused by micro-architectural effects into context with the shortcoming of low physical noise. Since the advanced attacks by Bronchain and Standaert exploit randomness reductions and profile with known randomness, a successful key recovery is still very likely.

In this case, more relaxed adversary models and a higher number of shares can be revisited. These evaluations can be conducted both in theory with the formal model from [43], as already outlined by Bronchain and Standaert in their paper, and with further practical evaluations. This investigation is meant

to either back-up or contradict the pessimistic outlook by Bronchain and Standaert which suggests that the effectiveness of masking on devices with low physical noise is limited in the face of strong adversary assumptions. If this can not be contradicted, parallel hardware architectures with a higher level of noise are, if available, the only hope for such devices. In this case, retrofitting side-channel security with software masking is impossible.

A laboratory evaluation of the proposed attack and countermeasure analysis is not part of this report. Instead, this work is left open for future efforts.

### 3.3 Read-out Protection Bypass Attacks

Microcontrollers usually have an integrated debug interface which is used to aid development, initial commissioning, and debugging of a system. This interface provides access to the internals of a microcontroller, including its flash memory and SRAM, which often contain valuable IP, cryptographic credentials, or other sensitive data.

The component that restricts access to the internals of a microcontroller via the debug interface is called read-out protection. A simple implementation of a read-out protection allows only the irreversible disabling of all debug access. However, depending on the application and product life cycle, this is not always desired. For failure analysis or return management in general, debug access to certain internals is often necessary and desired by the manufacturer of a product. To enable manufacturers to analyze defective products returned by customers, some microcontrollers support multiple protection levels with different access restrictions. For example, access to the internal SRAM is allowed for failure analysis while the nonvolatile flash memory, which usually contains the IP and other sensitive data, remains inaccessible via the debug interface. In case the debug interface is not irreversibly disabled, different methods for reactivation exist. Some implementations allow to reactivate the debug interface only after erasing all data on the microcontroller. Others allow password-based or even more sophisticated challenge-response based approaches based on symmetric or even public-key cryptography. Another example where the debug interface cannot be fully disabled and a more complex read-out protection is necessary is when multiple parties are involved in the firmware development process. Since applications become more and more complex, the firmware is sometimes not developed by one company but the product of multiple software components provided by different companies. To protect the IP of all involved parties during the development process, more sophisticated read-out protection techniques are needed in order to protect the individual IPs on a microcontroller.

Since the debug interface provides access to the internals of a microcontroller, attacking this interface is a valuable target for adversaries. The ultimate goal of an adversary is to gain unlimited access and bypass the read-out protection completely. However, depending on the application a microcontroller is used for, partial access might be sufficient, for example only to the internal SRAM or some CPU registers.

Attacks against read-out protection techniques can be split into the two categories **physical** and **non-physical**, depending on whether physical manipulations, temporary or permanent, are used or not.

**Non-physical Attacks.** Attacks that do not require physical tampering of a device are categorized as non-physical attacks. They are characterized by exploiting vulnerabilities caused by either the implementation of a read-out protection or even a conceptual weakness.

One example for exploiting an implementation flaw in a read-out protection is a race condition found in the STM32F0 microcontroller series from STMicroelectronics [68]. After the power-up of this microcontroller, there is a short time period in which the debug protection is not yet active. If an adversary is able to connect to the debug interface fast enough and perform a read operation before the protection becomes active, the flash memory can be read out. Since the time span the protection is inactive is very

short, the microcontroller needs to be power-cycled for every read operation. With this approach, the entire flash memory, including the containing IP and other sensitive data, can be read out in just a few minutes.

A conceptual weakness of a read-out protection feature was discovered for the nRF52, CKS32F1, and GD32VF1 microcontroller series [47],[69]. These devices are equipped with a read-out protection feature that, when activated, restricts access to the internal flash memory via the debug interface. However, access to the internal SRAM and the CPU remains possible. This approach has the drawback that it allows an adversary to access temporary credentials stored in SRAM or CPU registers. But even more problematic is that this design can be exploited to bypass the read-out protection and gain access to the flash memory. By placing a load instruction into the SRAM and instruct the CPU to execute it, the access restriction to the flash memory can be circumvented. The trick is to use a load instruction such that the CPU loads data from flash memory into the SRAM, which is accessible to the adversary. Another conceptual weakness was discovered in the STM32F1 series [87]. Similar to the previous approach, only direct access to the flash memory via the debug interface is blocked. However, the partial debug access is sufficient to exploit a vulnerability that leaks content of the flash memory through the PC register. This attack allows to extract large parts of the non-volatile flash memory and thus poses a threat to the containing IP and cryptographic secrets.

A common implementation for read-out protection techniques is that a reactivation of the debug interface first performs a mass erase of all internal memories. This ensures that sensitive information stored on a microcontroller is erased before the debug access is available again. The Atmel SAM7xC and Texas Instruments CC2400 series are only two examples for microcontrollers that implement this feature. One characteristic of these two microcontrollers is that reactivating the debug interface erases the flash memory content but not the SRAM [41],[52]. As a consequence, sensitive data in SRAM is accessible to an adversary after reactivating the debug interface.

Another conceptual weakness has been identified in an IP protection technique based on execute-only memory (XOM) which is integrated in a wide range of microcontrollers. This feature allows that multiple parties can sequentially develop and deploy firmware on a microcontroller without being able to copy the firmware of the other parties but being able to use it. In [86], the authors show that a specific execution of the protected code combined with information on the CPU registers and the SRAM is sufficient to recover the code stored in the XOM.

The presented non-physical attacks show how diverse the different implementations of read-out protections are and that even very restrictive access to the internals of a microcontroller can be exploited to gain access to sensitive information. These attacks are very powerful and require no special equipment, only tools every firmware developer uses for daily work.

**Physical Attacks.** In contrast to the previous attacks, physical attacks tamper with the behavior of the underlying hardware implementations of a read-out protection. A physical attack can further be categorized into *non-invasive*, *semi- invasive*, and *invasive*:

- Non-invasive attacks do not require modifications of the device. Methods in this category are, for example, voltage or clock glitching, and EMFI.

- Semi-invasive attacks need preparation of the device under attack, such as decapsulation. LFI and other optical attacks are examples for this category.

- Invasive attacks also require chip decapsulation but further need preparations such as removal of the passivation layer of the chip. Invasive attacks range from cheaper attacks like probing of the on-chip interconnects to more sophisticated and expensive attacks like *chip surgery* using a focused ion beam (FIB). Due to the high effort and cost of invasive attacks they are not largely represented in attacks on COTS microcontrollers.

Non-invasive attacks to fully bypass the read-out protection have been shown for the nRF52 and EFM32 microcontroller series [54],[55],[57],[88]. The read-out protection can be temporarily disabled by applying a voltage glitch or injecting a pulse via EMFI during the power-up phase of the microcontrollers. The underlying shortcomings that lead to this effect are not fully understood and remain unknown. This is not unusual for physical attacks, especially when the underlying hardware implementation is a black-box.

Nevertheless, in some cases the effects are fully understood, for example, an attack on the read-out protection of the STM32L4 microcontroller series [88]. This attack exploits a design flaw, which leads the hardware to downgrade the protection level, if an error during the transfer of configuration data from flash memory into an internal register is detected. By injecting a fault via EMFI at a specific time during the startup phase of the microcontroller this protection downgrade can be triggered. It is still not fully understood how the induced fault propagates, but how the system reacts to the occurrence of an error can be derived from the public documents.

Another non-invasive attack vector that tampers with the read-out protection was discovered by Schink et al. in [88]. As mentioned earlier, some implementations allow to reactivate the debug interface only after performing a mass erase of all memory blocks of a microcontroller, which are usually flash memory and SRAM.

The reactivation process consists of two phases: first, all the memory of the microcontroller is erased. Second, the debug interface is reactivated. The authors show that by injecting a pulse via EMFI into the first phase, the erase procedure can be interrupted and the flash memory content remains intact. The effect is that the erase procedure is skipped while the second phase, the debug interface reactivation, is still executed. After this attack, the adversary has full debug access to the microcontroller and the internal flash memory. So far, this attack has only been demonstrated on the STM32L4 microcontroller, but other devices could also be vulnerable since this kind of debug reactivation can be found in various COTS microcontrollers.

Semi-invasive attacks against read-out protections have been demonstrated on the STM32F1 and GD32F1 microcontroller series [68],[69]. By applying UV light on a decapsulated STM32F1 microcontroller, the protection level stored in flash memory can be downgraded, which reactivates the debug interface. In [69], the authors demonstrate an active and passive semi-invasive attack on the read-out protection of the GD32F1 microcontroller series from Giga Device. In contrast to other devices, its flash memory is located on a separate chip within the package. This design choice enables passive probing attacks by intercepting the inter-die bonding wires between memory and microcontroller. This allows an adversary to gain access to the content of the flash memory despite the enabled read-out protection. Also, an active attack has been demonstrated that manipulates the data transfer between flash memory and microcontroller. The attacker modifies the data signals between both chips in order to change the read-out protection configuration. This allows the read-out protection level to be downgraded and the debug interface to be re-enabled.

The examples of physical attacks show that even if there are no design or implementation flaws, read-out protections can be circumvented. Even fully deactivated debug interfaces can be reactivated by precisely injecting faults or carefully opening the chip package or tamper with the interconnection between chips. Even though not all effects of the physical attacks are fully understood, these attacks are still very effective and reproducible.

#### 3.3.1 Countermeasures

Attacks on the read-out protection of microcontrollers are severe because, if successful, they provide direct access to the internals of the device. In contrast to attacks on the control flow of an application or exploitation of side-channel leakage, the firmware on the microcontroller is usually not involved. As a result, retrofittable countermeasures are not able to prevent these attacks but, depending on the application a microcontroller is used for, may complicate them or even fully stop their effects and provide a sufficient

level of protection. In order to prevent attacks via the debug interface, well and carefully thought-out readout protection designs and implementations that take hardware attacks into account are necessary.

Exemplary mitigations that can be retrofitted either purely through software or using existing hardware features of microcontrollers are presented. In general, effective countermeasures against attacks on the read-out protection are very specific to the used microcontroller and its application, so this subject can not be covered completely.

Software-based Mitigation. One exemplary attack where software-based mitigation is possible is the exploitation of data leakage through the PC register, which enables read access to the flash memory content [87]. Exploiting this vulnerability does not allow an adversary to read the entire flash memory, small memory regions remain inaccessible. This peculiarity allows a very specific mitigation approach: the flash memory content can be organized in such a way that small amounts of data, for example, cryptographic credentials are placed in memory regions inaccessible for the adversary. Another example is the attack that exploits load instructions to copy the flash memory content into the SRAM that is accessible to the adversary [54], [55]. Here, the entire flash memory can be extracted and as the firmware on the microcontroller is never executed while the attack is carried out, there is no universal countermeasure that can prevent this attack or its effects. However, depending on the application of the microcontroller and the assets to be protected, different countermeasures are possible. In an application where the firmware and its IP needs to be protected, code obfuscation techniques, as presented in [28],[45], are possible to make reusing and reverse engineering of the firmware more complicated. The authors of [28] propose to use a physical unclonable identifier as unique secret that determines the order of instructions. If the firmware is copied to a different device, the order of instructions would be incorrect. The authors of [28],[45] derive reasonable high brute-force complexities. However, it is unclear how much easier an attack gets if the adversary tries more complex re-combination approaches than simple brute-force. Further, the practicality of such approaches without having dedicated hardware available is questionable.

In an application where protecting cryptographic secrets is the ultimate goal, more effective software-based countermeasures may be possible. For example, in case of hardware security tokens, the secrets used for authentication can be stored encrypted in flash memory. During an authentication, the token owner is asked for a password or passphrase to decrypt the secrets on-demand, as suggested in [88].

**Hardware-backed Mitigation**. An example for a countermeasure that requires special device features and thus depends on the used microcontroller is suggested in [88]. Here, the authors propose to store credentials in a dedicated SRAM that can be accessed via the debug interface only when the read-out protection is fully disabled. Another example for an application and device specific countermeasure is also presented in [88]. In this use case, it is necessary for the adversary to execute the application code such that the secret credentials, stored in the read-out protected flash memory, are transferred into the SRAM where they are accessible via the debug interface. The authors propose a mitigation approach that checks the state of the read-out protection and refuses further operation if the debug interface is not fully disabled. This does not completely prevent the attack but complicates it. The adversary needs to mount an additional and time consuming attack step to skip this check. Depending on the threat model this countermeasure might already provide sufficient protection.

#### 3.3.2 Attack Proposal and Countermeasure Evaluation

Since read-out protection mechanisms differ from manufacturer to manufacturer or even within individual product families, attacks are usually very tailored to a specific implementation. The identification of a potential vulnerability and the subsequent evaluation in a laboratory can take a long time. With the goal to evaluate the security of as much devices as possible, this report focuses the investigation on vulnerabilities that potentially affect multiple device families of a single or even multiple manufacturers.

The attack on the flash erase operation after unlocking the debug interface presented by Schink et al. in [88] was demonstrated on a single microcontroller family but has the potential to affect a wide range of products. The attack is also very severe since it threatens the confidentiality of the entire flash memory content and thus affects both IP and cryptographic secrets. The underlying effect of this attack is unclear but could affect a variety of devices. The attack was originally demonstrated on an STM32L4 from STMicroelectronics but other manufacturers, such as Silicon Labs and Nordic Semiconductor, have microcontrollers with similar features.

For a practical evaluation, first the results of Schink et al. are reproduced on the STM32L4 microcontroller family. The laboratory setup and results are described in Section 4.1. The original publication [88] provides information on the reliability of the attack working on a single device in their dedicated experimental setup. However, reproducibility on other STM32L4 microcontrollers and the influence of setup parameters, for example the position of the injection coil, remain unclear. Since the adversary deliberately triggers a mass erase of the flash memory and thereby potentially erases all IP and credentials on the device, the assets are irreversibly lost if the disruption is not successful. After the results on the STM32L4 are reproduced, the attack is investigated on other microcontrollers from STMicroelectronics. The idea behind this approach is that the hardware module that is used for the unlocking and erase procedure is the same among the microcontroller families. This report also analyses the effect of the attack on devices from other manufacturers, preference given to vendors identified during the market analysis. In the original publication, EMFI is used to disrupt the erasing procedure. This was adapted for the laboratory evaluation in this report (see Section 4.1). Future work should investigate whether voltage glitching is also suitable for this attack. Voltage glitching would reduce the attack costs and might be more robust and reliable since only precise timing is required. The positioning of the injection coil, which usually has to be done very precisely, would no longer be necessary.

Since software-based countermeasures to prevent attacks on the read-out protection are very application and device dependent, there is no general countermeasure or mitigation technique. Instead, countermeasures must be tailored to each affected device and product built on top of it. For example, there might be affected microcontrollers with special peripherals or features to irrevocably prevent the debug interface from being unlocked. Therefore, the laboratory evaluation in Section 4.1 does not include an evaluation of countermeasures.

### 4 Laboratory Evaluation

Based on the analysis of hardware attacks in Chapter 3, two of the three proposed attacks were chosen for practical investigation. In the following chapter, the results of this evaluation are presented. In Section 4.1, the evaluation results of an attack that targets a microcontroller's read-out protection are shown. For this attack, the repeatability on different devices is extremely important. Therefore, the laboratory setup and its building blocks, which are used to achieve a high accuracy, are described in detail. In Section 4.2, the results of evaluating a compiler-based countermeasure against control flow manipulation attacks are shown. For this attack, the repeatability is less of an issue. A similar setup as for the read-out protection attack can be used.

### 4.1 Flash Erase Suppression

In Section 3.3, a non-invasive attack demonstrated by Schink et al. that targets the read-out protection of STM32L4 microcontrollers [88] was described. The attack is presented as part of a comprehensive analysis of open source hardware security tokens. It is only discussed in this context and without a general in-depth analysis. However, the attack itself is also of general interest because, if successful, it provides unrestricted access to all secrets stored on the microcontroller's internal flash memory. Further, other microcontrollers of the STM32 family or even microcontrollers of other manufacturers may be susceptible to this attack vector. For that reason, this attack is reproduced and further details on its practicality are provided in this report.

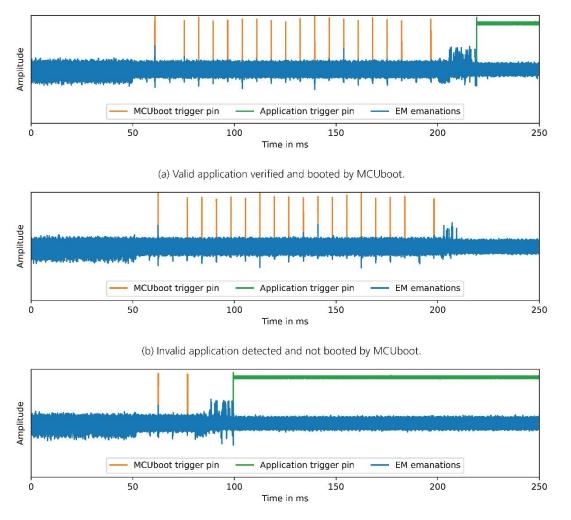

The STM32L4 microcontroller family features three read-out protection levels. In level 0, the read-out protection is disabled. In level 1, debug access is possible but with the restriction that any read attempt through the debug interface to the flash memory is blocked. Level 2 fully deactivates the debug interface. The attack presented by Schink et al. targets level 1. In the following, it is assumed that the microcontroller is in level 1. This assumption can be made as the authors of [88] also demonstrate how to downgrade from level 2 to 1. Thus a reactivation of the debug interface can be achieved. The attack that is reproduced here leverages that the read-out protection can always be disabled by changing the level to 0. Before the read-out protection is disabled, the device performs a mass erase in order to ensure that all sensitive content stored in the flash memory is erased. As described by the authors, the unlocking process consists of two phases. First, the flash content is erased and afterwards the read-out protection is deactivated. Schink et al. discovered that by injecting an electromagnetic fault into the first phase, the flash erase operation can be suppressed while the second phase is still executed. The attacker obtains a microcontroller with disabled read-out protection (level 0) and intact flash memory contents.

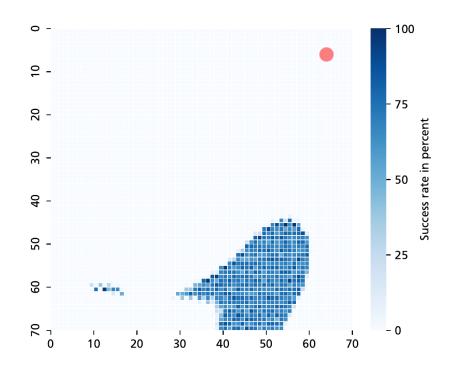

The downside of this attack vector is that, if the attack does not succeed, the adversary loses the flash memory content irretrievably. If the adversary attempts to steal a specific device individual secret, the attack irrevocably failed. If, however, IP or other information that is redundant on all devices of a product series is the target of the attack, an adversary has as many tries as devices in their possession. In both scenarios, the reliability of this attack vector is important. Schink et al. state a success rate of 100 % for this attack. However, they do not provide the exact position of the fault injection coil but only a schematic of the chip package and the coil position. For EMFI, such parameters may have a high impact on the success rate of the attack. Small changes from the actual position can lead to failure of the attack. With the laboratory evaluation in this section, detailed findings on the necessary precision for this attack vector are reported for the first time. Further, it is evaluated whether other microcontrollers are susceptible to this attack vector.

#### 4.1.1 Laboratory setup and Results

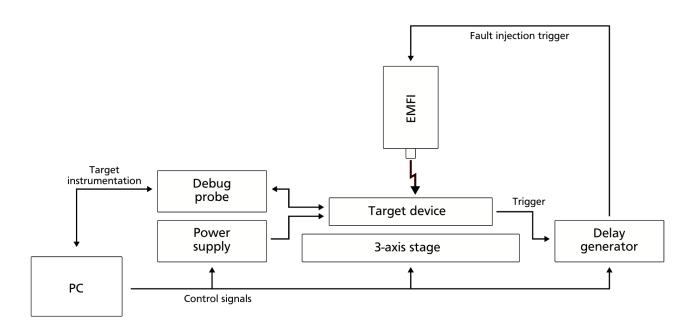

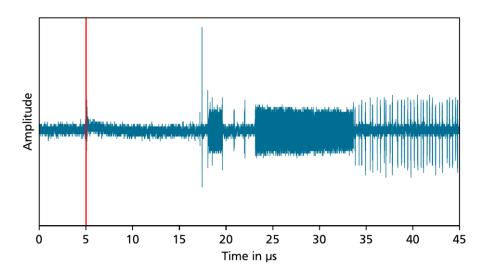

In order to reproduce the results of Schink et al., a similar laboratory setup with the same fault injection equipment, namely the ChipSHOUTER from NewAE and the included 4 mm CW injection coil, is used. All